# ACS APPLIED MATERIALS & INTERFACES

Threshold voltage (V)

# Electrical Characteristics of Metal Catalyst-Assisted Etched Rough Silicon Nanowire Depending on the Diameter Size

Sang Hoon Lee,<sup>||,†</sup> Tae Il Lee,<sup>||,§</sup> Su Jeong Lee,<sup>†</sup> Sang Myung Lee,<sup>‡</sup> Ilgu Yun,<sup>‡</sup> and Jae Min Myoung<sup>\*,†</sup>

<sup>†</sup>Department of Materials Science and Engineering, <sup>‡</sup>Department of Electrical and Electronic Engineering, Yonsei University, Seoul, Korea

<sup>§</sup>Department of BioNano Technology, Gachon University, Seongnam, Korea

Supporting Information

180 ABSTRACT: The dependence of electrical properties of rough and cylindrical Si nanowires (NWs) synthesized by ŝ 160 <sup>5</sup> 160 N /<sub>2</sub>m<sub>2</sub>) 140 diameter-controllable metal catalyst-assisted etching (MCE) on the size of the NW's diameter was demonstrated. Using a decal-printing and transfer process assisted by Al<sub>2</sub>O<sub>3</sub> sacrificial 120 Mobility layer, the Si NW field effect transistor (FET) embedded in a 100 polyvinylphenol adhesive and dielectric layer were fabricated. As the diameter of Si NW increased, the mobility of FET 80 increased from 80.51 to 170.95 cm<sup>2</sup>/V·s and the threshold 105 120 135 150 165 180 SI NW FET voltage moved from -7.17 to 0 V because phonon-electron The diameter of circular Si nanowire (nm) wave function overlaps, surface scattering, and defect scattering decreased and gate coupling increased as the ratio of surfaceto-volume got reduced.

KEYWORDS: silicon nanowires, diameter modulation, transfer method, field effect transistor, dielectrophorestic alignment

# 1. INTRODUCTION

Silicon nanowires (Si NWs) have been widely studied as building blocks for nanoscale semiconductor devices, such as field effect transistors (FETs),<sup>1-4</sup> photosensors,<sup>5</sup> solar cells,<sup>6–10</sup> biosensors,<sup>11–14</sup> and light-emitting diodes.<sup>15–17</sup> Two approaches for the synthesis of Si NWs have been developed: the vapor-liquid-solid (VLS) and the metal catalyst assisted etching (MCE) method.<sup>18-22</sup>

The VLS method is one of the most commonly used bottomup routes; when this method is used, the diameter of NWs can be controlled by modulating the size of seed particles, and doped NWs can be obtained by adding the selected species in the precursor gas.<sup>23</sup> A variety of Si NWs synthesized through the VLS method have been already experimentally and theoretically studied and reported.<sup>24,25</sup> However, NWs obtained through VLS are compositionally contaminated by the carbonaceous byproducts originating from metal-organic precursors or by seed metal elements.<sup>26,27</sup> In addition, the elemental metal seed diffuses into the NWs during their growth, acting as an impurity. In case of Si NWs, Au used as a metal seed element intrudes into the NWs and acts as a deep level acceptor. This chemical contamination has detrimental effects on the device performance.<sup>28-30</sup>

On the other hand, when the MCE method is used, Si NWs are directly formed from a Si wafer, without any contamination and with a uniform distribution of dopant. However, the surface properties of Si NWs synthesized using the MCE methods have not been thoroughly investigated so far. Si NWs achieved by MCE show a rougher surface than those synthesized by VLS; it is commonly believed that superficial defects and dangling bonds may degrade the properties of devices based on Si NWs. In particular, since Si NWs present a higher surface-to-volume ratio when they are characterized by a reduced diameter, the surface roughness of NWs dominantly affects the device properties and they could be changed by the circumstance surrounding NWs. In the present study, we fabricated FETs using the rough Si NWs synthesized through the MCE process and we investigate that the electrical properties of transistor can be modulated by controlling the diameter of a cylindrical Si NW. The rough Si NWs were synthesized by using our previously reported MCE process,<sup>31</sup> which allows to modulate the NW diameter without the need of any lithographic technique. To fabricate the Si NW-based transistor, each NW was addressed onto the electrodes by dielectrophoretic (DEP) alignment method on Al<sub>2</sub>O<sub>3</sub> film, used as a sacrificial transfer layer, and then, each NW was printed on poly(vinylphenol) (PVP), used as an adhesive and dielectric layer.

# 2. RESULTS AND DISCUSSION

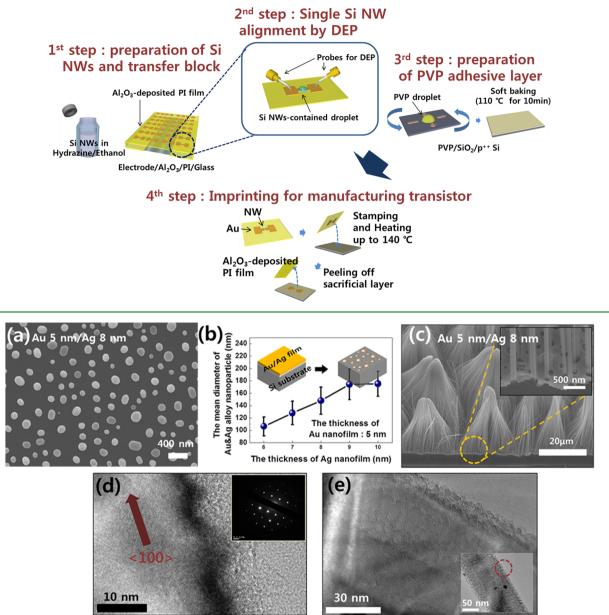

A four-step method for the fabrication of a Si NWs FET by direct printing using Al<sub>2</sub>O<sub>3</sub> as a sacrificial transfer layer is illustrated in Scheme 1. In the first step, p-type cylindrical Si NWs were synthesized by using the MCE method allowing to control their diameter and then stored in 99.9% ethanol

Received: October 28, 2014 Accepted: December 19, 2014 Published: December 19, 2014 Scheme 1. Process Flow Sequence to Decal-Printing and Fabrication of Cylindrical-Shaped Si NWs FET Using Al<sub>2</sub>O<sub>3</sub> Layer As a Sacrificial Transfer Layer

**Figure 1.** Formation of Au and Ag alloy nanoparticles in various thickness of Ag layer and synthesized cylindrical Si NWs. (a) A top view SEM image of Au and Ag alloy nanoparicles after rapid thermal annealing with 5 nm/8 nm in the thickness of Au/Ag layers. (b) The relationship between the Ag thickness and the nanoparticle diameter after annealing. (c)  $45^{\circ}$ -tilted SEM images of typical Si NWs formed with 5 and 8 nm in the thickness of Au/Ag layers and the shows a magnified SEM image of the circle area. (d) A TEM image of a single-crystalline with  $\langle 100 \rangle$  direction. (e) Rough surface of cylindrical Si NW synthesized by MCE process.

solution. Au electrodes were defined on  $Al_2O_3$ -coated flexible polyimide (PI) substrates by photolithography. In the second step, the Si NWs were addressed onto the Au electrodes by DEP alignment. In the third and the fourth steps, the Si NWs addressed onto the Au electrodes were decal-printed on a PVP adhesive layer, which was previously spin-coated on a commercial p<sup>++</sup> Si wafer with a 300 nm-thick SiO<sub>2</sub> layer and soft baked at 110 °C for 10 min. Finally, the cylindrical Si NW FETs were completed.

Figure 1a shows a scanning electron microscopy (SEM) image of Au/Ag alloy nanoparticles on Si substrates after annealing, with the original Au and Ag film thicknesses of 5 and

8 nm, respectively. When the Ag thin film deposited on Si substrate is annealed by rapid thermal annealing (RTA), the Ag nanoparticles, which present a poor adhesion to the substrate, tend to move across the surface during etching process, resulting in coalescence phenomena. Thus, in the present work, the Au film was additionally deposited onto the Ag film and the annealing was conducted to form Au/Ag alloy nanoparticles. According to the phase diagrams of Ag–Si and Au–Si, the Ag–Si eutectic temperature is beyond the RTA temperature, which is 700  $^{\circ}$ C, whereas the Au–Si eutectic reaction occurs under this temperature, so that the adhesion force between the nanoparticles and the Si substrate is enhanced.<sup>32,33</sup> Figure 1b

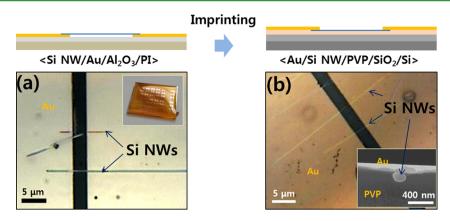

**Figure 2.** DEP and imprinting processes for transistor fabrication. (a) An OM image of Si NWs addressed on Au electrodes by DEP process and the inset is the digital photo image of a sacrificial transfer specimen. (b) An OM image of the transferred Si NWs and Au electrodes on to PVP adhesive layer; inset is the cross-sectional SEM image of Si NWs embedded in PVP layer and Au electrodes on it.

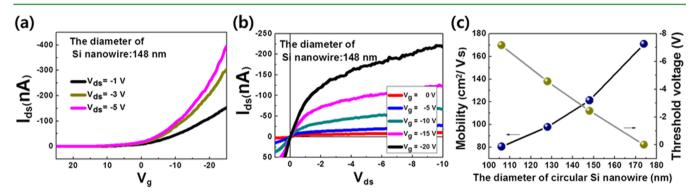

Figure 3. Electrical properties of imprinted single cylindrical Si NW FET. (a) Transfer and (b) output characteristics of the Si NW transistor with diameter of 148 nm. (c) Mobility and threshold voltage change as a function of the diameter of cylindrical Si NW.

shows that cylindrical Si NWs synthesized from Au/Ag films with a thickness of 5 and 6 nm, respectively, resulted in a mean nanoparticle diameter of 108 nm, whereas for film thicknesses of 5 and 7 nm, the mean diameter was 128 nm; for 5 and 8 nm, it was 147.9 nm; for 5 and 9 nm, it was 174.3 nm; and for 5 and 10 nm, it was 175 nm. The mean nanoparticle diameter increased linearly as the Ag film thickness increased. However, the specimen with a 10 nm Ag film thickness showed almost the same mean nanoparticle diameter compared to that with a 9 nm Ag film thickness, and the value of the mean diameter reached the saturation at about 175 nm. Furthermore, vertically aligned 40  $\mu$ m-long Si NWs with a high aspect ratio (~800) were produced via the second MCE process, which lasted for 3 h; Figure 1c shows Si NWs synthesized with film thicknesses of 5 and 8 nm for Au and Ag, respectively. After cutting, the Si NWs were dispersed in a solution of dilute hydrazine and ethanol, in order to prevent surface oxidation. Without dilute hydrazine, the surface of Si nanowires was easily oxidized to be SiO<sub>2</sub> and it made contact resistance between Si nanowires and Au electrodes increased. Thus, the carrier injection from Au electrode to the Si nanowire was disturbed at the interface with high contact resistance, and it caused poor transfer characteristic, as shown in Figure S1 in the Supporting Information.

The microstructure of the synthesized Si NWs was characterized by using a high-resolution transmission electron microscopy (HRTEM). Figure 1d indicates that Si NWs were produced along the  $\langle 100 \rangle$  direction and they were single crystals, as evident in the electron diffraction pattern shown in

the inset of Figure 1d. The Si NWs formed through our MCE method had a rough surface, as shown in Figure 1e.

Figure 2a shows an optical microscopy (OM) image of the cylindrical NWs connected to the Au electrodes having a 3  $\mu$ m gap; the inset is a digital photo image of the specimen, showing the structure of the device, made of Si NWs/Au electrodes/ Al<sub>2</sub>O<sub>3</sub>/PI substrate. The DEP process depends on the dielectric medium, the density of NWs in the medium, the bias on-time, and the strength of the bias field. Here, Al<sub>2</sub>O<sub>3</sub> was used as a sacrificial transfer layer and Au electrodes were defined onto it. The electric field used for the DEP process is supposed to be strong between the Au electrodes, whereas no leakage is expected in the other directions. Moreover, Al<sub>2</sub>O<sub>3</sub> has a high dielectric constant (9.0-10.1); therefore, the electric field can be directly formed between the Au electrodes.<sup>34</sup> The number of Si NWs connected to the Au electrodes per unit of time increased with increasing the density of Si NWs in the dispersion solution, which was used as a dielectric medium. The conditions for the DEP were optimized in order to allow the alignment of one or two Si NWs for 3 s. Figure 2b is the top view OM image of the Si NWs and electrodes transferred on PVP/SiO<sub>2</sub>/p<sup>++</sup> Si wafer, the inset is the cross-sectional SEM image of the device, showing that the cylindrical Si NWs were embedded in the PVP adhesive polymer layer.

Transistors based on Si NWs with different diameters (108, 128, 148, and 174 nm) were fabricated and their electrical properties were measured. From the top view of SEM image and the cross-sectional OM image of the device shown in Figure 2b, the active channel length and width of the sample

## **ACS Applied Materials & Interfaces**

were verified. The channel lengths were 3  $\mu$ m for all the samples, whereas the channel widths were equal to the diameter of the employed Si NWs (Si NWs were assumed to have a two-dimensional structure). The values of the capacitance for the gate dielectric were simulated by Silvaco, along to the diameter of cylindrical Si NWs embedded into the PVP layer (see Figure S2, Supporting Information). The transfer  $(I_{ds}-V_g)$  and the output  $(I_{ds}-V_{ds})$  curve for the p-channel transistor with single Si NWs (148 nm diameter) are shown in Figure 3a and b. An on/off current ratio of  $8.17 \times 10^3$  was obtained with a threshold voltage  $(V_{th})$  of -2.44 V; the transconductance was measured to be 0.0127  $\mu$ S at a  $V_{ds}$  of -5 V. The p-type linear field-effect mobility  $(\mu_h)$  of each device was calculated by using the equation:

$$\mu_{\rm h} = L/(WC_{\rm d}V_{\rm ds})g_{\rm m} \tag{1}$$

where *L* is the gap distance between the electrodes, *W* is the channel width of the device, equal to the diameter of the employed Si NWs,  $C_d$  represents the capacitance per unit area of the gate dielectric, whose value is 425 pF/cm<sup>2</sup>, and  $g_m$  is the transconductance. The mobility  $\mu_h$  was determined to be 121.24 cm<sup>2</sup>/(V s). The output characteristic was measured at various  $V_g$  values from 0 to -20 V in steps of -5 V.  $I_{ds}$  increased as the applied  $V_g$  increased and reached saturation as the  $V_{ds}$  increased, which is consistent with the performance of a typical p-channel transistor and implies a good ohmic contact between the Au electrode and the Si NW.

Figure 3c shows the changes in mobility and threshold voltage of the FET as the diameter of the cylindrical Si NW used as channel increases. It was already reported in other papers that the mobility is enhanced by an increase in the diameter of the Si NW, according to the following relation:<sup>35</sup>

$$\mu \propto d^2 m_{\rm eff}^{-1.5} \tag{2}$$

where *d* is the diameter of the Si NW and  $m_{\rm eff}$  is the effective mass of a hole. The mobility decreases as the Si NWs become thinner because the huge surface-to-volume ratio causes not only an increase in the phonon–electron wave function overlaps, surface scattering, and defect scattering but also a decrease in the gate coupling.

Si NWs synthesized by the MCE method cause a strong positive surface charge because of the defects and dangling bonds present on the NWs rough surface. This positive surface charge is balanced by a negative charge in the depletion region to accomplish charge neutrality. If the positive surface charge gets stronger, the depletion region becomes larger, so that the effective conduction area is reduced. Since the etching solutions used in the present work had all the same concentration, it is reasonable to assume that the surface roughness of Si NWs with different diameters was identical. Therefore, they had similar values of positive surface charge caused by the surface roughness of NWs, and the effective area of NWs became larger with increasing the Si NW diameter. In other words, the increase in current observed for Si NWs with larger diameters could be caused by the larger cross-sectional area, indicating a reduction in carrier scattering with an increase in diameter. The mobility values were determined to be 80.51, 97.84, 121.24, and  $170.95 \text{ cm}^2/(\text{V s})$  for diameters of 108, 128, 148, and 174 nm, respectively. This proportional relationship between mobility and diameter is very similar to that in FET with Si NWs synthesized by VLS. $^{35,36}$

The threshold voltage is also controlled by the surface roughness of cylindrical Si NWs. If Si NWs were embedded in PVP, the excess carrier concentration in the conduction channel at the interface between PVP and Si NWs was reduced by the presence of  $OH^-$  ions, and a scattering effect caused by carrier trapping at the interface occurred. Generally, the positive charge density on the surface of Si NWs increases the conduction of the NWs, whereas the negative charge density decreases the conduction and makes the threshold voltage higher.<sup>37</sup> The change of the threshold voltage according to the variation in the Si NW diameter could be induced by the following equation of mobility and conductance in Si NWs:

$$G = \frac{q\mu_{\rm n}}{L} \int_{A} n \, \mathrm{d}A \tag{3}$$

where G is the conductance, L is the nanowire length, q is the electron charge,  $\mu_n$  is the electron mobility, A is cross sectional area, and n is the electron density for each element.<sup>38</sup> As mentioned above, the mobility is proportional to the square of the diameter of the Si NWs. From this relationship, it could be inferred that the conductance is enhanced and the threshold voltage is reduced with an increment in the diameter of the NWs; the threshold voltages were determined to be -7.17, -4.55, -2.44, and 0 V for NWs having diameters of 108, 128, 148, and 174 nm, respectively. The transfer  $(I_{ds}-V_g)$  curve obtained for different diameters of Si NWs is shown in Figure S3 (Supporting Information); it was experimentally confirmed that  $V_{ds}$  increased and  $V_{th}$  was shifted toward 0 V as the Si NW diameter increased.

## 3. EXPERIMENTAL SECTION

Synthesis of Diameter Controllable Circular Si NWs. Si NWs were synthesized by diameter controllable MCE method from a boron-doped p-type Si (100) wafer with resistivity of  $1-10 \Omega \cdot cm$ . The process for synthesis of the Si NWs has been reported in our previous work.<sup>31</sup> The development point from previous process is that Au on Ag double layer was deposited on Si wafer at the first step to enhance the adhesion property between Si substrate and nanoparticles formed through RTA process instead using Ag single layer. In order to control the diameters of circular Si NWs, the thickness of evaporated Ag layer is changed from 6 to 10 nm in the steps of 1 and 5 nm in the thickness of Au layer was individually deposited on Ag layer by e-beam evaporator. The next processes including annealing process were conducted by the same methods with the previous work. The synthesized circular Si NWs were dispersed in the solution of hydrazine and 99.9% ethanol solution (1:500 v/v).

Formation of Al<sub>2</sub>O<sub>3</sub> Sacrificial Layer and Au Electrodes. To prepare the sacrificial layer for this study, slide glass and 15  $\mu$ m-thick PI substrates were cut into 2 cm  $\times$  2.5 and 3 cm  $\times$  3.5 cm pieces, respectively. The flexible PI substrate wrapped the slide glass and attached on it in order not to be folded or winkled. Flexible PI substrate wrapping slide glass was cleaned in 99.9% acetone, 99.9% methanol, and deionized (DI) water by sonication for 10 min. Then, 20 nm-thick Al<sub>2</sub>O<sub>3</sub> was deposited on PI substrate by e-beam evaporator with a deposition rate of 0.3 Å/s. Then, PR solution (AZ5214E) was spin-coated on Al<sub>2</sub>O<sub>3</sub>-deposited PI substrate with 500 rpm for 5 s and 2500 rpm for 45 s and baked at 110  $^\circ C$  for 50 s in order to form electrodes pattern with a 3  $\mu$ m gap. The exposure time was confirmed to be 6 s, and PR was developed in developer solution (AZ MIF 300) for 27 s. After rinsing with DI water and drying the specimen with nitrogen gas, a 40 nm-thick Au layer was deposited on the PR pattern formed by photolithography. By stripping the PR pattern with sonication in 99.9% acetone for 2 min and rinsing the specimen with 99.9% methanol and DI water, Au electrodes with a 3  $\mu m$  gap were defined. Then, the surfaces of the Au electrodes were cleaned by O<sub>2</sub> plasma treatment with 300 W, 50 sccm, 20 Pa, and 5

## **ACS Applied Materials & Interfaces**

min of power, flow rate of  $O_2$ , working pressure, and operation time, respectively, in order to completely remove the residual on Au electrodes.

Dielectrophoretic Alignment of Si Nanowires on Au Electrodes. DEP alignment method was applied to address prepared Si NWs between Au electrodes. After synthesizing and cutting Si NWs, they were dispersed in the solution of hydrazine and ethanol by sonication for 10 min and the dilute dispersion solution had about  $7 \times 108$  NWs/mL. Through the sonication and dilution processes, the bundle of Si NWs could be separated and individual Si NWs were aligned between Au electrodes by DEP method. After suspending a 4  $\mu$ L of solution droplet containing Si NWs on Au electrodes, direct current (DC) bias with a frequency of 1 kHz, amplitude of 10 Vpp and a pulse width of 500  $\mu$ s was applied on the electrodes for 3 s in order for one or two Si NWs to be aligned and connected between electrodes.<sup>39</sup>

Transfer Layer Formation and Direct Printing. To get high yield of printing and stable device properties, PVP was applied as not only a polymeric adhesive agent but also a dielectric layer for gate insulator. First of all, 10% PVP solution and a cross-linking agent, poly(melamine-co-formaldehyde) (PMCF), in propylene glycolmonomethyl ether acetate (PGMEA) was coated onto thermally oxidized p<sup>++</sup> Si substrate with 300 nm-thick SiO<sub>2</sub> layer. PVP layers spin-coated on Si substrate with the condition of 500 rpm for 5 s and 5000 rpm for 120 s were softly baked at 110 °C for 10 min. A Si NWs-addressed PI substrate at the second step was separated from slide glass for imprinting and transferring process. Separated PI substrate was flipped over and stamped onto softly baked PVP layer at the third step and heated up from 110 to 140 °C with an increasing rate of 2 °C/min. Au electrodes and addressed Si NWs were transferred into PVP layer by detaching the Al<sub>2</sub>O<sub>2</sub>-deposited PI substrate and fabrication of circular Si NW FET was completed by baking PVP in vacuum at 175 °C for 1 h.

## 4. CONCLUSION

In summary, we fabricated a FET with Si NWs synthesized through the MCE process and we investigated the dependence of the electrical properties, such as mobility and threshold voltage, on the NW diameter. Cylindrical Si NWs were synthesized as previously reported, using a Au and Ag double layer instead of a Ag single layer. For the fabrication of the Si NW-based FET, cylindrical Si NWs with diameters of 108, 128, 148, and 174 nm were connected between Au electrodes using the DEP process and then decal-printed on PVP-coated on p<sup>++</sup> Si substrate with 300 nm-thick SiO<sub>2</sub>. Findings show that the mobility of devices increased while the threshold voltage decreased with increasing the Si NW diameter, because the surface-to-volume ratio decreased, whereas the defects characterizing the rough surface were not influential.

# ASSOCIATED CONTENT

#### Supporting Information

Electrical property (transfer curve) of Si NW FET without hydrazine treatment. Additional information for simulated capacitance values and transfer characteristic of Si NW FET according to various diameters of Si nanowire. This material is available free of charge via the Internet at http://pubs.acs.org.

## AUTHOR INFORMATION

### **Corresponding Author**

\*E-mail: jmmyoung@yonsei.ac.kr.

Author Contributions

<sup>II</sup>S.H.L. and T.I.L. contributed equally.

Notes

The authors declare no competing financial interest.

## ACKNOWLEDGMENTS

This research was supported by WCU program through the National Research Foundation of Korea funded by the Ministry of Education, Science and Technology [*R*32-20031] and by the LG Display academic industrial cooperation program.

## REFERENCES

(1) Lauhon, L. J.; Gudiksen, M. S.; Wang, C. L.; Lieber, C. M. Epitaxial Core–Shell and Core–Multishell Nanowire Heterostructures. *Nature* 2002, 420, 57–61.

(2) Cui, Y.; Zhong, Z. H.; Wang, D. L.; Wang, W. U.; Lieber, C. M. High Performance Silicon Nanowire Field Effect Transistors. *Nano Lett.* **2003**, *3*, 149–152.

(3) Xiang, J.; Lu, W.; Hu, Y. J.; Wu, Y.; Yan, H.; Lieber, C. M. Ge/Si Nanowire Heterostructures as High-Performance Field-Effect Transistors. *Nature* **2006**, *441*, 489–493.

(4) Zheng, G. F.; Lu, W.; Jin, S.; Lieber, C. M. Synthesis and Fabrication of High-Performance n-Type Silicon Nanowire Transistors. *Adv. Mater.* 2004, *16*, 1890–1893.

(5) Bae, J.; Kim, H.; Zhang, X. M.; Dang, C. H.; Zhang, Y.; Choi, Y. J.; Nurmikko, A.; Wang, Z. L. Si Nanowire Metal-Insulator-Semiconductor Photodetectors as Efficient Light Harvesters. *Nanotechnology* **2010**, *21*, 095502.

(6) Tian, B. Z.; Zheng, X. L.; Kempa, T. J.; Fang, Y.; Yu, N. F.; Yu, G. H.; Huang, J. L.; Lieber, C. M. Coaxial Silicon Nanowires as Solar Cells and Nanoelectronic Power Sources. *Nature* 2007, 449, 885–888.

(7) Garnett, E. C.; Yang, P. D. Silicon Nanowire Radial p-n Junction Solar Cells. *J. Am. Chem. Soc.* 2008, 130, 9224–9225.

(8) Garnett, E.; Yang, P. D. Light Trapping in Silicon Nanowire Solar Cells. *Nano Lett.* **2010**, *10*, 1082–1087.

(9) Sivakov, V.; Andra, G.; Gawlik, A.; Berger, A.; Plentz, J.; Falk, F.; Christiansen, S. H. Silicon Nanowire-Based Solar Cells on Glass: Synthesis, Optical Properties, and Cell Parameters. *Nano Lett.* **2009**, *9*, 1549–1554.

(10) Tian, B.; Kempa, T. J.; Lieber, C. M. Single Nanowire Photovoltaics. *Chem. Soc. Rev.* **2009**, *38*, 16–24.

(11) Patolsky, F.; Lieber, C. M. Nanowire Nanosensors. *Mater. Today* 2005, *8*, 20–28.

(12) Cui, Y.; Wei, Q. Q.; Park, H. K.; Lieber, C. M. Nanowire Nanosensors for Highly Sensitive and Selective Detection of Biological and Chemical Species. *Science* **2001**, *293*, 1289–1292.

(13) Hakim, M. A.; Lombardini, M.; Sun, K.; Giustiniano, F.; Roach, P. L.; Davies, D. E.; Howarth, P. H.; de Planque, M. R.; Morgan, H.; Ashburn, P. Thin Film Polycrystalline Silicon Nanowire Biosensors. *Nano Lett.* **2012**, *12*, 1868–1872.

(14) Zhang, G. J.; Chua, J. H.; Chee, R. E.; Agarwal, A.; Wong, S. M.; Buddharaju, K. D.; Balasubramanian, N. Highly Sensitive Measurements of PNA-DNA Hybridization using Oxide-Etched Silicon Nanowire Biosensors. *Biosens. Bioelectron.* **2008**, *23*, 1701–1707.

(15) Park, H. G.; Barrelet, C. J.; Wu, Y. N.; Tian, B. Z.; Qian, F.; Lieber, C. M. A Wavelength-Selective Photonic-Crystal Waveguide Coupled to a Nanowire Light Source. *Nat. Photonics* **2008**, *2*, 622– 626.

(16) Hayden, O.; Greytak, A. B.; Bell, D. C. Core-Shell Nanowire Light-Emitting Diodes. *Adv. Mater.* **2005**, *17*, 701–704.

(17) Huang, Y.; Duan, X. F.; Lieber, C. M. Nanowires for Integrated Multicolor Nanophotonics. *Small* **2005**, *1*, 142–147.

(18) Chartier, C.; Bastide, S.; Levy-Clement, C. Metal-Assisted Chemical Etching of Silicon in HF-H<sub>2</sub>O<sub>2</sub>. *Electrochim. Acta* **2008**, *53*, 5509–5516.

(19) Levy-Clement, C.; Wang, X. D.; Benoit-Moez, C.; Elias, J.; Philippe, L.; Michler, J. Applications of Colloidal Crystal Patterning for Synthesis of 1D and 3D Nanostructured Semiconductors. *Phys. Status Solidi A* **2011**, 208, 1426–1432.

(20) Peng, K. Q.; Wu, Y.; Fang, H.; Zhong, X. Y.; Xu, Y.; Zhu, J. Uniform, Axial-Orientation Alignment of One-Dimensional Single-Crystal Silicon Nanostructure Arrays. *Angew. Chem., Int. Ed.* **2005**, *44*, 2737–2742.

## **ACS Applied Materials & Interfaces**

(21) Peng, K. Q.; Zhang, M. L.; Lu, A. J.; Wong, N. B.; Zhang, R. Q.; Lee, S. T. Ordered Silicon Nanowire Arrays via Nanosphere Lithography and Metal-Induced Etching. *Appl. Phys. Lett.* **2007**, *90*, 163123.

(22) de Boor, J.; Geyer, N.; Wittemann, J. V.; Gosele, U.; Schmidt, V. Sub-100 nm Silicon Nanowires by Laser Interference Lithography and Metal-Assisted Etching. *Nanotechnology* **2010**, *21*, 095302.

(23) Duffy, R.; Shayesteh, M.; McCarthy, B.; Blake, A.; White, M.; Scully, J.; Yu, R.; Kelleher, A. M.; Schmidt, M.; Petkov, N.; Pelaz, L.; Marqué, L. A. The Curious Case of Thin-Body Ge Crystallization. *Appl. Phys. Lett.* **2011**, *99*, 131910.

(24) Jo, G.; Hong, W. K.; Maeng, J.; Park, M. W.; Lee, T. Logic Inverters Composed of Controlled Depletion-Mode and Enhancement-Mode ZnO Nanowire Transistor. *Appl. Phys. Lett.* **2009**, *94*, 173118.

(25) Li, C.; Zhang, D. H.; Han, S.; Liu, X. L.; Tang, T.; Zhou, C. W. Diameter-Controlled Growth of Single-Crystalline  $In_2O_3$  Nanowires and Their Electronic Properties. *Adv. Mater.* **2003**, *15*, 143–146.

(26) Hanrath, T.; Korgel, B. A. Nucleation and Growth of Germanium Nanowires Seeded by Organic Monolayer-Coated Gold Nanocrystals. J. Am. Chem. Soc. 2002, 124, 1424–1429.

(27) Zaitseva, N.; Harper, J.; Gerion, D.; Saw, C. Unseeded Growth of Germanium Nanowires by Vapor-Liquid-Solid Mechanism. *Appl. Phys. Lett.* **2005**, *86*, 053105.

(28) Collins, C. B.; Carlson, R. O.; Gallagher, C. J. Properties of Gold-Doped Silicon. *Phys. Rev.* **1957**, *105*, 1168–1173.

(29) Fahey, P. M.; Griffin, P. B.; Plummer, J. D. Point Defects and Dopant Diffusion in Silicon. *Rev. Mod. Phys.* **1989**, *61*, 289–384.

(30) Koren, E.; Elias, G.; Boag, A.; Hemesath, E. R.; Lauhon, L. J.; Rosenwaks, Y. Direct Measurement of Individual Deep Traps in Single Silicon Nanowires. *Nano Lett.* **2011**, *11*, 2499–2502.

(31) Lee, S. H.; Lee, T. I.; Moon, K. J.; Myoung, J. M. A Route for Modulating the Diameter of Cylindrical Silicon Nanowires by using Thermal Self-Ordering Silver Nanoparticles. *ACS Appl. Mater. Interfaces* **2013**, *5*, 11777–11782.

(32) Oleslnski, R. W.; Gokhale, A. B.; Abbaschlan, G. J. The Ag-Si (silver-silicon) System. Bull. Alloy Phase Diagrams 1986, 10, 635–639.

(33) Gerlach, W.; Goel, B. Gold Silicon Phase Diagram. Solid-State Electron. 1967, 10, 589-592.

(34) Hashizume, T.; Ootomo, S.; Hasegawa, H. Suppression of Current Collapse in Insulated Gate AlGaN/GaN Heterostructure Field-Effect Transistors using Ultrathin  $Al_2O_3$  Dielectric. *Appl. Phys. Lett.* **2003**, 83, 2952–2954.

(35) Buin, A. K.; Verma, A.; Svizhenko, A.; Anantram, M. P. Significant Enhancement of Hole Mobiliity in [110] Silicon Nanowires compared to Electrons and Bulk Silicon. *Nano Lett.* **2008**, *8*, 760–765.

(36) Motayed, A.; Vaudin, M.; Davydov, A. Diameter Dependent Transport Properties of Gallium Nitride Nanowire Field Effect Transistors. *Appl. Phys. Lett.* **2007**, *90*, 043104.

(37) Moon, J. M.; Lee, T. I.; Lee, W.; Myoung, J. M. Logic Inverters Based on the Property Modulated Si Nanowires by Controlled Surface Modifications. J. Mater. Chem. **2012**, *22*, 1527–1531.

(38) Elfstrom, N.; Juhasz, R.; Sychugov, I.; Engfeldt, T.; Karlstrom, A. E.; Linnros, J. Surface Charge Sensitivity of Silicon Nanowires: Size Dependence. *Nano Lett.* **2007**, *7*, 2608–2612.

(39) Lee, T. I.; Choi, W. J.; Moon, K. J.; Choi, J. H.; Kar, J. P.; Das, S. N.; Kim, Y. S.; Baik, H. K.; Myoung, J. M. Programmable Direct-Printing Nanowire Electronic Components. *Nano Lett.* **2010**, *10*, 1016–1021.